### APPENDIX

# A

## LOGIC CIRCUITS

Information in digital computers is represented and processed by electronic networks called *logic circuits*. These circuits operate on *binary variables* that assume one of two distinct values, usually called 0 and 1. In this appendix we will give a concise presentation of logic functions and circuits for their implementation, including a brief review of integrated circuit technology.

#### **A.1** BASIC LOGIC FUNCTIONS

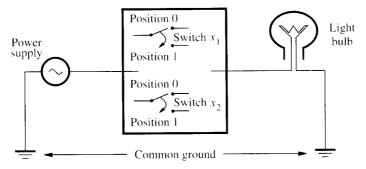

It is helpful to introduce the topic of binary logic by examining a practical problem that arises in all homes. Consider a lightbulb whose on/off status is controlled by two switches,  $x_1$  and  $x_2$ . Each switch can be in one of two possible positions, 0 or 1, as shown in Figure A.1a. It can thus be represented by a binary variable. We will let the switch names serve as the names of the associated binary variables. The figure also shows an electrical power supply and a lightbulb. The way the switch terminals are interconnected determines how the switches control the light. The light will be on only if a closed path exists from the power supply through the switch network to the lightbulb. Let a binary variable f represent the condition of the light. If the light is on, f = 1, and if the light is off, f = 0. Thus, f = 1 means that there is at least one closed path through the network, and f = 0 means that there is no closed path. Clearly, f is a function of the two variables  $x_1$  and  $x_2$ .

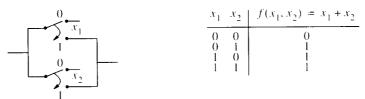

Let us consider some possibilities for controlling the light. First, suppose that the light is to be on if either switch is in the 1 position, that is, f = 1 if

$$x_1 = 1$$

and  $x_2 = 0$

or

$$x_1 = 0$$

and  $x_2 = 1$

or

$$x_1 = 1$$

and  $x_2 = 1$

The connections that implement this type of control are shown in Figure A.1b. A logic truth table that represents this situation is shown beside the wiring diagram. The table lists all possible switch settings along with the value of f for each setting. In logic terms, this table represents the OR function of the two variables  $x_1$  and  $x_2$ . The operation is represented algebraically by a "+" sign or a " $\vee$ " sign, so that

$$f = x_1 + x_2 = x_1 \vee x_2$$

We say that  $x_1$  and  $x_2$  are the *input* variables and f is the *output* function.

We should point out some basic properties of the OR operation. It is commutative, that is,

$$x_1 + x_2 = x_2 + x_1$$

(a) Light bulb controlled by two switches

(b) Parallel connection (OR control)

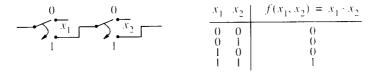

(c) Series connection (AND control)

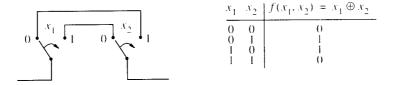

(d) EXCLUSIVE-OR connection (XOR control)

Figure A.1 Light switch example.

It can be extended to n variables, so that

$$f = x_1 + x_2 + \dots + x_n$$

has the value 1 if any variable  $x_i$  has the value 1. This represents the effect of connecting more switches in parallel with the two switches in Figure A.1b. Also, inspection of the truth table shows that

$$1 + x = 1$$

and

$$0 + x = x$$

Now, suppose that the light is to be on only when both switches are in the 1 position. The connections for this, along with the corresponding truth-table representation, are shown in Figure A.1c. This is the AND function, which uses the symbol "·" or " $\wedge$ " and is denoted as

$$f = x_1 \cdot x_2 = x_1 \wedge x_2$$

Some basic properties of the AND operation are

$$x_1 \cdot x_2 = x_2 \cdot x_1$$

$$1 \cdot x = x$$

and

$$0 \cdot x = 0$$

The AND function also extends to *n* variables, with

$$f = x_1 \cdot x_2 \cdot \cdots \cdot x_n$$

having the value 1 only if all the  $x_i$  variables have the value 1. This represents the case in which more switches are connected in series with the two switches in Figure A.1c.

The final possibility that we will discuss for the way the switches determine the light status is another common situation. If we assume that the switches are at the two ends of a stairway, it should be possible to turn the light on or off from either switch. That is, if the light is on, changing either switch position should turn it off; and if it is off, changing either switch position should turn it on. Assume that the light is off when both switches are in the 0 position. Then changing either switch to the 1 position should turn the light on. Now suppose that the light is on with  $x_1 = 1$  and  $x_2 = 0$ . Switching  $x_1$  back to 0 will obviously turn the light off. Furthermore, it must be possible to turn the light off by changing  $x_2$  to 1, that is, f = 0 if  $x_1 = x_2 = 1$ . The connections to implement this type of control are shown in Figure A.1d. The corresponding logic operation is called the EXCLUSIVE-OR (XOR) function, which is represented by the symbol " $\oplus$ ". Some of its properties are

$$x_1 \oplus x_2 = x_2 \oplus x_1$$

$$1 \oplus x = \overline{x}$$

$$0 \oplus x = x$$

where  $\overline{x}$  denotes the NOT function of the variable x. This single-variable function,  $f = \overline{x}$ , has the value 1 if x = 0 and the value 0 if x = 1. We say that the input x is being *inverted* or *complemented*.

#### A.1.1 ELECTRONIC LOGIC GATES

The use of switches, closed or open electrical paths, and lightbulbs to illustrate the idea of logic variables and functions is convenient because of their familiarity and simplicity. The logic concepts that have been introduced are equally applicable to the electronic circuits used to process information in digital computers. The physical variables are electrical voltages and currents instead of switch positions and closed or open paths. For example, consider a circuit that is designed to operate on inputs that are at either +5 or 0 volts. The circuit outputs are also at either +5 or 0 V. Now, if we say that +5 V represents logic 1 and 0 V represents logic 0, then we can describe what the circuit does by specifying the truth table for the logic operation that it performs.

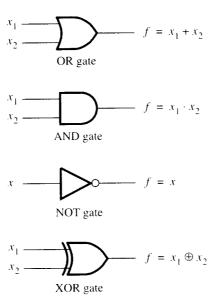

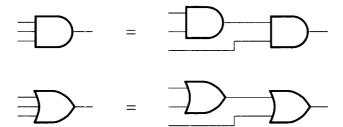

With the help of transistors, it is possible to design simple electronic circuits that perform logic operations such as AND, OR, XOR, and NOT. It is customary to use the name *gates* for these basic logic circuits. Standard symbols for these gates are shown in Figure A.2. A somewhat more compact graphical notation for the NOT operation

**Figure A.2** Standard logic gate symbols.

is used when inversion is applied to a logic gate input or output. In such cases, the inversion is denoted by a small circle.

The electronic implementation of logic gates will be discussed in Section A.5. We will now proceed to discuss how basic gates can be used to construct logic networks that implement more complex logic functions.

#### **A.2** SYNTHESIS OF LOGIC FUNCTIONS

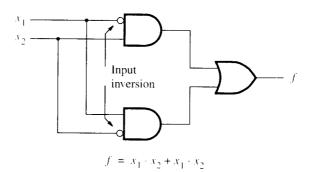

Consider the network composed of two AND gates and one OR gate that is shown in Figure A.3a. It can be represented by the expression

$$f = \overline{x}_1 \cdot x_2 + x_1 \cdot \overline{x}_2$$

The construction of the truth table for this expression is shown in Figure A.3b. First, the values of the AND terms are determined for each input valuation. Then the values of the function f are determined using the OR operation. The truth table for f is identical

(a) Network for the XOR function

| <i>x</i> <sub>1</sub> | X <sub>2</sub> | $x_1 \cdot x_2$ | $x_1 \cdot x_2$ | $f = x_1 \cdot x_2 + x_1 \cdot x_2$ $= x_1 \oplus x_2$ |

|-----------------------|----------------|-----------------|-----------------|--------------------------------------------------------|

| 0                     | 0              | 0               | 0               | 0                                                      |

| 0                     | 1              | 1               | 0               | 1                                                      |

| 1                     | 0              | 0               | 1               | 1                                                      |

| 1                     | 1              | 0               | 0               | 0                                                      |

(b) Truth table construction of  $x_1 \cdot x_2 + x_1 \cdot x_2$

Figure A.3 Implementation of the XOR function using AND, OR, and NOT gates.

Table A.1 Two 3-variable functions

| <i>x</i> <sub>1</sub> | <i>x</i> <sub>2</sub> | <i>x</i> <sub>3</sub> | fı | $f_2$ |

|-----------------------|-----------------------|-----------------------|----|-------|

| 0                     | 0                     | 0                     | 1  | 1     |

| 0                     | 0                     | 1                     | 1  | 1     |

| 0                     | I                     | 0                     | 0  | 1     |

| 0                     | 1                     | 1                     | 1  | 0     |

| 1                     | 0                     | 0                     | 0  | 1     |

| i                     | 0                     | 1                     | 0  | 1     |

| 1                     | 1                     | 0                     | 0  | 0     |

| 1                     | 1                     | 1                     | 1  | 0     |

|                       |                       |                       |    |       |

to the truth table for the XOR function, so the three-gate network in Figure A.3a is an implementation of the XOR function using AND, OR, and NOT gates. The logic expression  $\bar{x}_1 \cdot x_2 + x_1 \cdot \bar{x}_2$  is called a *sum-of-products* form because the OR operation is sometimes called the "sum" function and the AND operation the "product" function.

We should note that it would be more proper to write

$$f = ((\overline{x}_1) \cdot x_2) + (x_1 \cdot (\overline{x}_2))$$

to indicate the order of applying the operations in the expression. To simplify the appearance of such expressions, we define a hierarchy among the three operations AND, OR, and NOT. In the absence of parentheses, operations in a logic expression should be performed in the following order: NOT, AND, and then OR. Furthermore, it is customary to omit the "·" operator when there is no ambiguity.

Returning to the sum-of-products form, we will now explain how any logic function can be synthesized in this form directly from its truth table. Consider the truth table of Table A.1 and suppose we wish to synthesize the function  $f_1$  using AND, OR, and NOT gates. For each row of the table in which  $f_1 = 1$ , we include a product (AND) term in the sum-of-products form. The product term includes all three input variables. The NOT operator is applied to these variables individually so that the term is 1 only when the variables have the particular valuation that corresponds to that row of the truth table. This means that if  $x_i = 0$ , then  $\overline{x}_i$  is entered in the product term, and if  $x_i = 1$ , then  $x_i$  is entered. For example, the fourth row of the table has the function entry 1 for the input valuation

$$(x_1, x_2, x_3) = (0, 1, 1)$$

The product term corresponding to this is  $\overline{x}_1x_2x_3$ . Doing this for all rows in which the function  $f_1$  has the value 1 leads to

$$f_1 = \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 x_3 + \overline{x}_1 x_2 x_3 + x_1 x_2 x_3$$

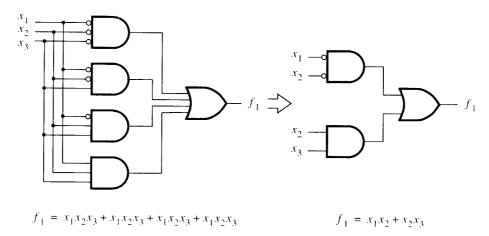

The logic network corresponding to this expression is shown on the left side in Figure A.4. As another example, the sum-of-products expression for the XOR function

**Figure A.4** A logic network for  $f_1$  of Table A.1 and an equivalent minimal network.

can be derived from its truth table using this technique. This approach can be used to derive sum-of-products expressions and the corresponding logic networks for truth tables of any size.

#### **A.3** MINIMIZATION OF LOGIC EXPRESSIONS

We have shown how to derive one sum-of-products expression for each truth table. In fact, there are many equivalent expressions and logic networks for any particular truth table. Two logic expressions or logic gate networks are equivalent if they have identical truth tables. An expression that is equivalent to the sum-of-products expression we derived for  $f_1$  in the previous section is

$$\overline{x}_1\overline{x}_2 + x_2x_3$$

To prove this, we construct the truth table for the simpler expression and show that it is identical to the truth table for  $f_1$  in Table A.1. This is done in Table A.2. The construction of the table for  $\overline{x}_1\overline{x}_2 + x_2x_3$  is done in three steps. First, the value of the product term  $\overline{x}_1\overline{x}_2$  is computed for each valuation of the inputs. Then  $x_2x_3$  is evaluated. Finally, these two columns are ORed together to obtain the truth table for the expression. This truth table is identical to the truth table for  $f_1$  given in Table A.1.

To simplify logic expressions we will perform a series of algebraic manipulations. The new logic rules that we will use in these manipulations are the distributive rule

$$w(y+z) = wy + wz$$

and the identity

| Table | Δ2 | Evaluation | of the | evnression | F. 72 | + rara |

|-------|----|------------|--------|------------|-------|--------|

|       |    |            |        |            |       |        |

| $x_1$ | <i>x</i> <sub>2</sub> | х3 | $\bar{x}_1\bar{x}_2$ | x <sub>2</sub> x <sub>3</sub> | $\overline{x}_1\overline{x}_2 + x_2x_3 = f_1$ |

|-------|-----------------------|----|----------------------|-------------------------------|-----------------------------------------------|

| 0     | 0                     | 0  | 1                    | 0                             | 1                                             |

| 0     | 0                     | 1  | 1                    | 0                             | 1                                             |

| 0     | 1                     | 0  | 0                    | 0                             | 0                                             |

| 0     | 1                     | 1  | 0                    | 1                             | 1                                             |

| 1     | 0                     | 0  | 0                    | 0                             | 0                                             |

| 1     | 0                     | 1  | 0                    | 0                             | 0                                             |

| 1     | 1                     | 0  | 0                    | 0                             | 0                                             |

| 1     | 1                     | 1  | 0                    | 1                             | I                                             |

| 1     | 1                     | 1  | 0                    | 1                             | ı                                             |

**Table A.3** Truth-table technique for proving equivalence of expressions

| w | y | z | y + z | Left-hand side $w(y+z)$ | wy | wz | Right-hand side<br>wy + wz |

|---|---|---|-------|-------------------------|----|----|----------------------------|

| 0 | 0 | 0 | 0     | 0                       | 0  | 0  | 0                          |

| 0 | 0 | 1 | 1     | 0                       | 0  | 0  | 0                          |

| 0 | 1 | 0 | 1     | 0                       | 0  | 0  | 0                          |

| 0 | i | 1 | 1     | 0                       | 0  | 0  | 0                          |

| 1 | 0 | 0 | 0     | 0                       | 0  | 0  | 0                          |

| 1 | 0 | 1 | 1     | 1                       | 0  | 1  | 1                          |

| 1 | 1 | 0 | 1     | 1                       | 1  | 0  | 1                          |

| 1 | I | 1 | 1     | 1                       | 1  | 1  | 1                          |

Table A.3 shows the truth-table proof of the distributive rule. It should now be clear that rules such as this can always be proved by constructing the truth tables for the left-hand side and the right-hand side to show that they are identical. Logic rules, such as the distributive rule, are sometimes called *identities*. Although we will not need to use it here, another form of distributive rule that we should include for completeness is

$$w + yz = (w + y)(w + z)$$

The objective in logic minimization is to reduce the cost of implementation of a given logic function according to some criterion. More particularly, we wish to start with a sum-of-products expression derived from a truth table and simplify it to an equivalent *minimal sum-of-products* expression. To define the criterion for minimization, it is necessary to introduce a size or cost measure for a sum-of-products expression. The

usual cost measure is a count of the total number of gates and gate inputs required in implementing the expression in the form shown in Figure A.4. For example, the larger expression in this figure has a cost of 21, composed of a total of 5 gates and 16 gate inputs. Input inversions are ignored in this counting process. The cost of the simpler expression is 9, composed of 3 gates and 6 inputs. We are now in a position to state that a sum-of-products expression is minimal if there is no other equivalent sum-of-products expression with a lower cost. In the simple examples that we will introduce, it is usually reasonably clear when we have arrived at a minimal expression. Thus, we will not give rigorous proofs of minimality.

The general strategy in performing algebraic manipulations to simplify a given expression is as follows. First, group product terms in pairs that differ only in that some variable appears complemented  $(\bar{x})$  in one term and true (x) in the other. When the common subproduct consisting of the other variables is factored out of the pair by the distributive rule, we are left with the term  $x + \bar{x}$ , which has the value 1. Applying this procedure to the first expression for  $f_1$ , we obtain

$$f_{1} = \overline{x}_{1}\overline{x}_{2}\overline{x}_{3} + \overline{x}_{1}\overline{x}_{2}x_{3} + \overline{x}_{1}x_{2}x_{3} + x_{1}x_{2}x_{3}$$

$$= \overline{x}_{1}\overline{x}_{2}(\overline{x}_{3} + x_{3}) + (\overline{x}_{1} + x_{1})x_{2}x_{3}$$

$$= \overline{x}_{1}\overline{x}_{2} \cdot 1 + 1 \cdot x_{2}x_{3}$$

$$= \overline{x}_{1}\overline{x}_{2} + x_{2}x_{3}$$

This expression is minimal. The network corresponding to it is shown in Figure A.4.

The grouping of terms in pairs so that minimization can lead to the simplest expression is not always as obvious as it is in the preceding example. A rule that is often helpful is

$$w + w = w$$

This allows us to repeat product terms so that a particular term can be combined with

Table A.4 Rules of binary logic

| w + y = y + w                                 | wy = yw                                                                                                                                                               |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (w+y)+z=w+(y+z)                               | (wy)z = w(yz)                                                                                                                                                         |

| w + yz = (w + y)(w + z)                       | w(y+z) = wy + wz                                                                                                                                                      |

| w + w = w                                     | ww = w                                                                                                                                                                |

| $\overline{\overline{w}} = w$                 |                                                                                                                                                                       |

| $w + \overline{w} = 1$                        | $w\overline{w} = 0$                                                                                                                                                   |

| $\overline{w+y} = \overline{w}  \overline{y}$ | $\overline{wy} = \overline{w} + \overline{y}$                                                                                                                         |

| 1+w=1                                         | $0 \cdot w = 0$                                                                                                                                                       |

| 0+w=w                                         | $1 \cdot w = w$                                                                                                                                                       |

|                                               | $(w + y) + z = w + (y + z)$ $w + yz = (w + y)(w + z)$ $w + w = w$ $\overline{w} = w$ $w + \overline{w} = 1$ $\overline{w + y} = \overline{w}\overline{y}$ $1 + w = 1$ |

more than one other term in the factoring process. As an example of this, consider the function  $f_2$  in Table A.1. The sum-of-products expression that can be derived for it directly from the truth table is

$$f_2 = \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 x_3 + \overline{x}_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 \overline{x}_3 + x_1 \overline{x}_2 x_3$$

By repeating the first product term  $\bar{x}_1\bar{x}_2\bar{x}_3$  and interchanging the order of terms (by the commutative rule), we obtain

$$f_2 = \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 x_3 + x_1 \overline{x}_2 \overline{x}_3 + x_1 \overline{x}_2 x_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 x_2 \overline{x}_3$$

Grouping the terms in pairs and factoring yields

$$f_2 = \overline{x}_1 \overline{x}_2 (\overline{x}_3 + x_3) + x_1 \overline{x}_2 (\overline{x}_3 + x_3) + \overline{x}_1 (\overline{x}_2 + x_2) \overline{x}_3$$

=  $\overline{x}_1 \overline{x}_2 + x_1 \overline{x}_2 + \overline{x}_1 \overline{x}_3$

The first pair of terms is again reduced by factoring, and we obtain the minimal expression

$$f_2 = \overline{x}_2 + \overline{x}_1 \overline{x}_3$$

This completes our discussion of algebraic simplification of logic expressions. The obvious practical application of this mathematical exercise stems from the fact that networks with fewer gates and inputs are cheaper and easier to implement. Therefore, it is of economic interest to be able to determine the minimal expression that is equivalent to a given expression. The rules that we have used in manipulating logic expressions are summarized in Table A.4. They are arranged in pairs to show their symmetry as they apply to both the AND and OR functions. So far, we have not had occasion to use either involution or de Morgan's rules, but they will be found to be useful in the next section.

#### **A.3.1** MINIMIZATION USING KARNAUGH MAPS

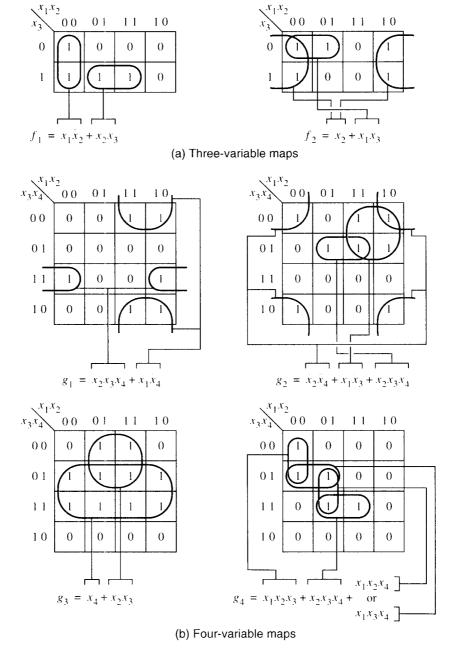

In our algebraic minimization of the functions  $f_1$  and  $f_2$  of Table A.1, it was necessary to guess the best way to proceed at certain points. For instance, the decision to repeat the term  $\bar{x}_1\bar{x}_2\bar{x}_3$  as the first step in minimizing  $f_2$  is not obvious. There is a geometric technique that can be used to quickly derive the minimal expression for a logic function of a few variables. The technique depends on a different form for presentation of the truth table, a form called the *Karnaugh map*. For a three-variable function, the map is a rectangle composed of eight squares arranged in two rows of four squares each, as shown in Figure A.5a. Each square of the map corresponds to a particular valuation of the input variables. For example, the third square of the top row represents the valuation  $(x_1, x_2, x_3) = (1, 1, 0)$ . Because there are eight rows in a three-variable truth table, the map obviously requires eight squares. The entries in the squares are the function values for the corresponding input valuations.

The key idea in the formation of the map is that horizontally and vertically adjacent squares correspond to input valuations that differ in only one variable. When two adjacent squares contain 1s, they indicate the possibility of an algebraic simplification.

Figure A.5 Minimization using Karnaugh maps.

In the map for  $f_2$  in Figure A.5a, the 1 values in the leftmost two squares of the top row correspond to the product terms  $\overline{x}_1\overline{x}_2\overline{x}_3$  and  $\overline{x}_1x_2\overline{x}_3$ . The simplification

$$\overline{x}_1\overline{x}_2\overline{x}_3 + \overline{x}_1x_2\overline{x}_3 = \overline{x}_1\overline{x}_3$$

was performed earlier in minimizing the algebraic expression for  $f_2$ . This simplification can be obtained directly from the map by grouping the two 1s as shown. The product term that corresponds to a group of squares is the product of the input variables whose values are constant on these squares. If the value of input variable  $x_i$  is 0 for all 1s of a group, then  $\overline{x_i}$  is entered in the product, but if  $x_i$  has the value 1 for all 1s of the group, then  $x_i$  is entered in the product. Adjacency of two squares includes the property that the left-end squares are adjacent to the right-end squares. Continuing with our discussion of  $f_2$ , the group of four 1s consisting of the left-end column and the right-end column simplifies to the single-variable term  $\overline{x_2}$  because  $x_2$  is the only variable whose value remains constant over the group. All four possible combinations of values of the other two variables occur in the group.

Karnaugh maps can be used for more than three variables. A Karnaugh map for four variables can be obtained from two 3-variable maps. Examples of four-variable maps are shown in Figure A.5b, along with minimal expressions for the functions represented by the maps. In addition to two- and four-square groupings, it is now possible to form eight-square groupings. Such a grouping is illustrated in the map for  $g_3$ . Note that the four corner squares constitute a valid group of four and are represented by the product term  $\overline{x}_2\overline{x}_4$  in  $g_2$ . As in the case of three-variable maps, the term that corresponds to a group of squares is the product of the variables whose values do not change over the group. For example, the grouping of four 1s in the upper right-hand corner of the map for  $g_2$  is represented by the product term  $x_1\overline{x}_3$  because  $x_1 = 1$  and  $x_3 = 0$  over the group. The variables  $x_2$  and  $x_4$  have all the possible combinations of values over this group. It is also possible to use Karnaugh maps for five-variable functions. In this case, two 4-variable maps are used, one of them corresponding to the 0 value for the fifth variable and the other corresponding to the 1 value.

The general procedure for forming groups of two, four, eight, and so on in Karnaugh maps is readily derived. Two adjacent pairs of 1s can be combined to form a group of four. Similarly, two adjacent groups of four can be combined to form a group of eight. In general, the number of squares in any valid group must be equal to  $2^k$ , where k is an integer.

We will now consider a procedure for using Karnaugh maps to obtain minimal sum-of-products expressions. As can be seen in the maps of Figure A.5, a large group of 1s corresponds to a small product term. Thus, a simple gate implementation results from covering all the 1s in the map with as few groups as possible. In general, we should choose the smallest set of groups, picking large ones wherever possible, that cover all the 1s in the map. Consider, for example, the function  $g_2$  in Figure A.5b. As we have already seen, the 1s in the four corners constitute a group of four that is represented by the product term  $\overline{x}_2\overline{x}_4$ . Another group of four exists in the upper right-hand corner and is represented by the term  $x_1\overline{x}_3$ . This covers all the 1s in the map except for the 1 in the square where  $(x_1, x_2, x_3, x_4) = (0, 1, 0, 1)$ . The largest group of 1s that includes this square is the two-square group represented by the term  $x_2\overline{x}_3x_4$ . Therefore, the minimal

expression for  $g_2$  is

$$g_2 = \overline{x}_2 \overline{x}_4 + x_1 \overline{x}_3 + x_2 \overline{x}_3 x_4$$

Minimal expressions for the other functions shown in the figure can be derived in a similar manner. Note that in the case of  $g_4$  there are two possible minimal expressions, one including the term  $\overline{x}_1x_2x_4$  and the other including the term  $\overline{x}_1\overline{x}_3x_4$ . It is often the case that a given function has more than one minimal expression.

In all our examples, it is relatively easy to derive minimal expressions. In general, there are formal algorithms for this process, but we will not consider them here.

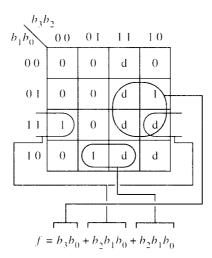

#### **A.3.2** DON'T-CARE CONDITIONS

In many situations, some valuations of the inputs to a digital circuit never occur. For example, consider the binary-coded decimal (BCD) number representation. Four binary variables  $b_3$ ,  $b_2$ ,  $b_1$ , and  $b_0$  represent the decimal digits 0 through 9, as shown in Figure A.6. These four variables have a total of 16 distinct valuations, only 10 of which are used for representing the decimal digits. The remaining valuations are not used. Therefore, any logic circuit that processes BCD data will never encounter any of these six valuations at its inputs.

Figure A.6 gives the truth table for a particular function that may be performed on a BCD digit. We do not care what the function values are for the unused input valuations; hence, they are called *don't-cares* and are denoted as such by the letter "d" in the truth table. To obtain a circuit implementation, the function values corresponding to don't-care conditions can be arbitrarily assigned to be either 0 or 1. The best way to assign them is in a manner that will lead to a minimal logic gate implementation. We should interpret don't-cares as 1s whenever they can be used to enlarge a group of 1s. Because larger groups correspond to smaller product terms, minimization is enhanced by the judicious inclusion of don't-care entries.

The function in Figure A.6 represents the following processing on a decimal digit input: The output f is to have the value 1 whenever the inputs represent a nonzero digit that is evenly divisible by 3. Three groups are necessary to cover the three 1s of the map, and don't-cares have been used to enlarge these groups as much as possible.

#### **A.4** SYNTHESIS WITH NAND AND NOR GATES

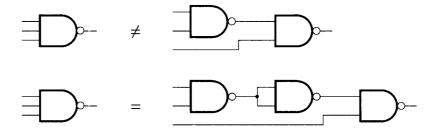

We will now consider two other basic logic gates called NAND and NOR, which are extensively used in practice because of their simple electronic realizations. The truth table for these gates is shown in Figure A.7. They implement the equivalent of the AND and OR functions followed by the NOT function, which is the motivation for the names and standard logic symbols for these gates. Letting the arrows "↑" and "↓" denote the NAND and NOR operators, respectively, and using de Morgan's rule in Table A.4.

| Decimal digit represented | Binary coding $b_3 b_2 b_1 b_0$ | f |

|---------------------------|---------------------------------|---|

| ()                        | 0 0 0 0                         | 0 |

| i                         | 0 0 0 1                         | 0 |

| 2                         | 0 0 1 0                         | 0 |

| 3                         | 0 0 1 1                         | 1 |

| 4                         | 0 1 0 0                         | 0 |

| 5                         | 0 1 0 1                         | 0 |

| 6                         | 0 1 1 0                         | 1 |

| 7                         | 0 1 1 1                         | 0 |

| 8                         | 1 0 0 0                         | 0 |

| 9                         | 1 0 0 1                         | 1 |

| ſ                         | 1 0 1 0                         | d |

|                           | 1 0 1 1                         | d |

| unuvad                    | 1 1 0 0                         | d |

| unused {                  | 1 1 0 1                         | d |

|                           | 1 1 1 0                         | d |

| l                         | 1 1 1 1                         | d |

**Figure A.6** Four-variable Karnaugh map illustrating don't cares.

we have

$$x_1 \uparrow x_2 = \overline{x_1 x_2} = \overline{x}_1 + \overline{x}_2$$

and

$$x_1 \downarrow x_2 = \overline{x_1 + x_2} = \overline{x}_1 \overline{x}_2$$

NAND and NOR gates with more than two input variables are available, and they

| $x_1$ $x_2$                | $f_{}$        | $x_1$ $x$                                                                      | f                   |

|----------------------------|---------------|--------------------------------------------------------------------------------|---------------------|

| 0 0<br>0 1<br>1 0<br>1 1   | 1             | 0 0                                                                            | 0 0 0 0             |

| 0 1                        | 1             | 0 1                                                                            | . 0                 |

| 1 0                        | 1             | 1 0                                                                            | 0                   |

| 1 1                        | 0             | 1 1                                                                            | . 0                 |

| $f = x_1 \uparrow x_2 = .$ |               |                                                                                | $= x_1 + x_2 = x_1$ |

| $x_1 - x_2 - x_2 - x_2$    | <b>)</b> o— f | $\begin{bmatrix} x_1 & \longrightarrow \\ x_2 & \longrightarrow \end{bmatrix}$ | <b>)</b> 0- f       |

$x_2$

(b) NOR

Figure A.7 NAND and NOR gates.

(a) NAND

operate according to the obvious generalization of de Morgan's law as

$$x_1 \uparrow x_2 \uparrow \cdots \uparrow x_n = \overline{x_1 x_2 \cdots x_n} = \overline{x}_1 + \overline{x}_2 + \cdots + \overline{x}_n$$

and

$$x_1 \downarrow x_2 \downarrow \cdots \downarrow x_n = \overline{x_1 + x_2 + \cdots + x_n} = \overline{x}_1 \overline{x}_2 \cdots \overline{x}_n$$

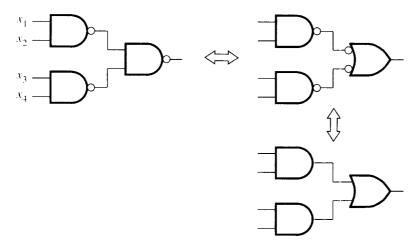

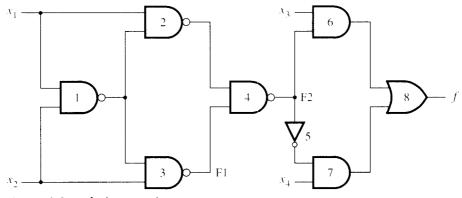

Logic design with NAND and NOR gates is not as straightforward as with AND, OR, and NOT gates. One of the main difficulties in the design process is that the associative rule is not valid for NAND and NOR operations. We will expand on this problem later. First, however, let us describe a simple, general procedure for synthesizing any logic function using only NAND gates. There is a direct way to translate a logic network expressed in sum-of-products form into an equivalent network composed only of NAND gates. The procedure is easily illustrated with the aid of an example. Consider the following algebraic manipulation of a logic expression corresponding to a four-input network composed of three 2-input NAND gates:

$$(x_1 \uparrow x_2) \uparrow (x_3 \uparrow x_4) = \overline{(x_1 x_2)(x_3 x_4)}$$

$$= \overline{x_1 x_2} + \overline{x_3 x_4}$$

$$= x_1 x_2 + x_3 x_4$$

We have used de Morgan's rule and the involution rule in this derivation. Figure A.8 shows the logic network equivalent of this derivation. Since any logic function can be synthesized in a sum-of-products (AND-OR) form and because the preceding derivation is obviously reversible, we have the result that any logic function can be synthesized in NAND-NAND form. We can see that this result is true for functions of any number of variables. The required number of inputs to the NAND gates is obviously the same as the number of inputs to the corresponding AND and OR gates.

Figure A.8 Equivalence of NAND-NAND and AND-OR networks.

Let us return to the comment that the nonassociativity of the NAND operator can be an annoyance. In designing logic networks with NAND gates using the procedure illustrated in Figure A.8, a requirement for a NAND gate with more inputs than can be found on standard commercially available gates may arise. If this happens when one is using AND and OR gates, there is no problem because the AND and OR operators are associative, and a straightforward cascade of limited fan-in gates can be used. The case of implementing three-input AND and OR functions with two-input gates is shown in Figure A.9a. The solution is not as simple in the case of NAND gates. For example, a three-input NAND function cannot be implemented by a cascade of 2 two-input NAND gates. Three gates are needed, as shown in Figure A.9b.

A discussion of the implementation of logic functions using only NOR gates proceeds in a similar manner. Any logic function can be synthesized in a product-of-sums (OR-AND) form. Such networks can be implemented by equivalent NOR-NOR networks.

The preceding discussion introduced some basic concepts in logic design. Detailed discussion of the subject can be found in any of a number of textbooks (see References 1, 3, 7–11).

It is important for the reader to appreciate that many different realizations of a given logic function are possible. For practical reasons, it is useful to find realizations that minimize the cost of implementation. It is also often necessary to minimize the propagation delay through a logic network. We introduced the concept of minimization in the previous sections to give an indication of the nature of logic synthesis and the reductions in cost that may be achieved. For example, Karnaugh maps graphically show the manipulation possibilities that lead to optimal solutions. Although it is important to understand the principles of optimization of logic networks, it is not necessary to do the optimization by hand. Sophisticated *computer-aided design* (CAD) programs exist for such synthesis. The designer needs to specify only the desired functional behavior, and the CAD software generates a cost-effective network that implements the required functionality.

(a) Implementing three-input AND and OR functions with two-input gates

(b) Implementing a three-input NAND function with two-input gates

Figure A.9 Cascading of gates.

#### A.5 Practical Implementation of Logic Gates

Let us now turn our attention to the means by which logic variables can be represented and logic functions can be implemented in practice. The choice of a physical parameter to represent logic variables is obviously technology-dependent. In electronic circuits, either voltage or current levels can be used for this purpose.

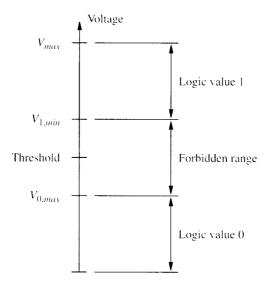

To establish a correspondence between voltage levels and logic values or states, the concept of a *threshold* is used. Voltages above a given threshold are taken to represent one logic value, with voltages below that threshold representing the other. In practical situations, the voltage at any point in an electronic circuit undergoes small random variations for a variety of reasons. Because of this "noise," the logic state corresponding to a voltage level near the threshold cannot be reliably determined. To avoid such ambiguity, a "forbidden range" should be established, as shown in Figure A.10. In this case, voltages below  $V_{0,max}$  represent the 0 value, and voltages above  $V_{1,min}$  represent the 1 value. In subsequent discussion, we will often use the terms "low" and "high" to represent the voltage levels corresponding to logic values 0 and 1, respectively.

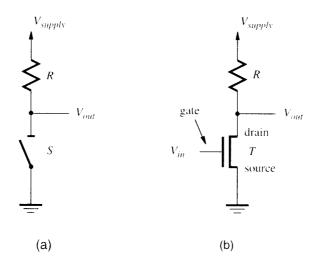

We will begin our discussion of electronic circuits that implement basic logic functions by considering simple circuits consisting of resistors and transistors that act as switches. Consider the circuits in Figure A.11. When switch S in Figure A.11a is closed, the output voltage  $V_{out}$  is equal to 0 (ground). When S is open, the output

Figure A.10 Representation of logic values by voltage levels.

Figure A.11 An inverter circuit.

voltage  $V_{out}$  is equal to the supply voltage,  $V_{supply}$ . The same effect can be obtained in Figure A.11b, in which a transistor T is used to replace the switch S. When the input voltage applied to the gate of the transistor is 0 (that is, when  $V_{in} = 0$ ), the transistor is equivalent to an open switch, and  $V_{out} = V_{supply}$ . When  $V_{in}$  changes to  $V_{supply}$ , the transistor acts as a closed switch and the output voltage  $V_{out}$  is very close to 0. Thus, the circuit performs the function of a logic NOT gate.

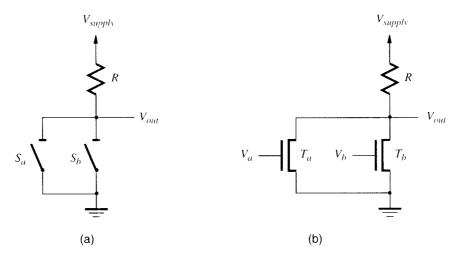

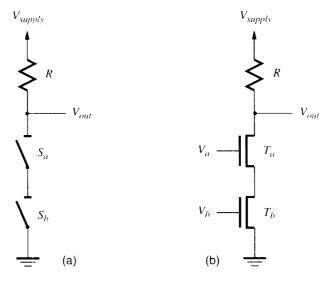

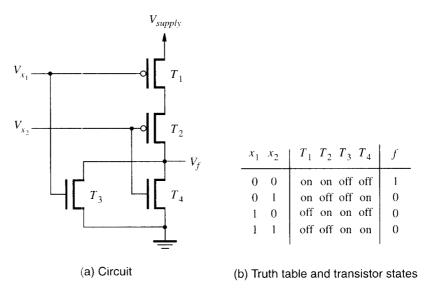

We can now discuss the implementation of more complex logic functions. Figure A.12 shows a circuit realization for a NOR gate. In this case,  $V_{out}$  in Figure A.12a is high only when both switches  $S_a$  and  $S_b$  are open. Similarly,  $V_{out}$  in Figure A.12b is high only when both inputs  $V_a$  and  $V_b$  are low. Thus, the circuit is equivalent to a NOR gate in which  $V_a$  and  $V_b$  correspond to two logic variables  $x_1$  and  $x_2$ . We can easily verify that a NAND gate can be obtained by connecting the transistors in series as shown in Figure A.13. The logic functions AND and OR can be implemented using NAND and NOR gates, respectively, followed by the inverter of Figure A.11.

Figure A.12 A transistor circuit implementation of a NOR gate.

Figure A.13 A transistor circuit implementation of a NAND gate.

Note that NAND and NOR gates are simpler in their circuit implementations than AND and OR gates. Hence, it is not surprising to find that practical realizations of logic functions use NAND and NOR gates extensively. Many of the examples given in this book show circuits consisting of AND, OR, and NOT gates for ease of understanding. In practice, logic circuits contain all five types of gates.

#### **A.5.1 CMOS CIRCUITS**

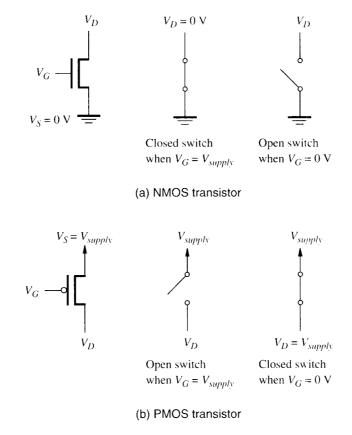

Figures A.11 through A.13 illustrate the general structure of circuits implemented using *NMOS technology*. The name derives from the fact that the transistors used to realize the logic functions are of NMOS type. Two types of *metal-oxide semiconductor* (MOS) transistors are available for use as switches. An n-channel transistor is said to be of NMOS-type, and it behaves as a closed switch when its gate input is raised to the positive power supply voltage,  $V_{supply}$ , as indicated in Figure A.14a. The opposite behavior is achieved with a p-channel transistor, which is said to be of PMOS type. It acts as an open switch when the gate voltage,  $V_G$ , is equal to  $V_{supply}$ , and as a closed switch

Figure A.14 NMOS and PMOS transistors in logic circuits.

when  $V_G = 0$ , as indicated in Figure A.14b. Note that the graphical symbol for a PMOS transistor has a bubble on the gate input to indicate that its behavior is complementary to that of an NMOS transistor. Note also that the names source and drain are associated with the opposite terminals of PMOS transistors in comparison with NMOS transistors. The source of an NMOS transistor is connected to ground, while the source of a PMOS transistor is connected to  $V_{supply}$ . This naming convention is due to the nature of the current that flows through these transistors.

A drawback of the circuits in Figures A.11 through A.13 is their power consumption. In the state in which the switches are closed to provide a path between ground and the pull-up resistor R, there is current flowing from  $V_{supply}$  to ground. In the opposite state, in which switches are open, there is no path to ground and there is no current flowing. (In MOS transistors no current flows through the gate terminal.) Thus, depending on the states of its gates, there may be significant power consumption in a logic circuit.

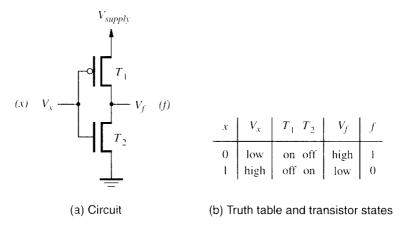

An effective solution to the power consumption problem lies in using both NMOS and PMOS transistors to implement circuits that do not dissipate power when in a steady state. This approach leads to the CMOS (complementary metal-oxide semiconductor) technology. The basic idea of CMOS circuits is illustrated by the inverter circuit in Figure A.15. When  $V_x = V_{supply}$ , which corresponds to the input x having the logic value 1, transistor  $T_1$  is turned off and  $T_2$  is turned on. Thus,  $T_2$  pulls the output voltage  $V_f$  down to 0. When  $V_x$  changes to 0, transistor  $T_1$  turns on and  $T_2$  turns off. Thus,  $T_1$  pulls the output voltage  $V_f$  up to  $V_{supply}$ . Therefore, the logic values of x and y are complements of each other, and the circuit implements a NOT gate.

A key feature of this circuit is that transistors  $T_1$  and  $T_2$  operate in a complementary fashion; when one is on, the other is off. Hence, there is always a closed path from the output point f to either  $V_{supply}$  or ground. There is no closed path between  $V_{supply}$  and ground at any time except during a very short transition period when the transistors are changing their states. This means that the circuit does not dissipate appreciable power when it is in a steady state. It dissipates power only when it is switching from one logic

Figure A.15 CMOS realization of a NOT gate.

Figure A.16 Structure of a CMOS circuit.

state to another. Therefore, power dissipation in this circuit is dependent on the rate at which state changes take place.

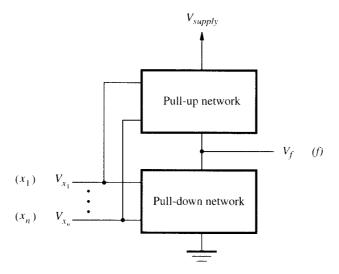

We can now extend the CMOS concept to circuits that have n inputs, as shown in Figure A.16. NMOS transistors are used to implement the pull-down network, such that a closed path is established between the output point f and ground when a desired function  $F(x_1, \ldots, x_n)$  is equal to 0. The pull-up network is built with PMOS transistors, such that a closed path is established between the output f and  $V_{supply}$  when  $F(x_1, \ldots, x_n)$  is equal to 1. The pull-up and pull-down networks are functional complements of each other, so that in steady state there exists a closed path only between the output f and either  $V_{supply}$  or ground, but not both.

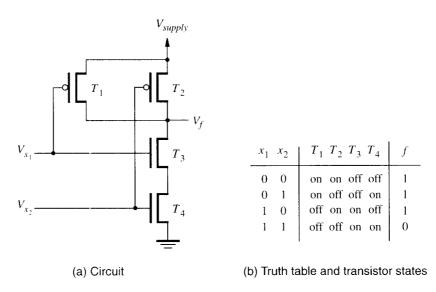

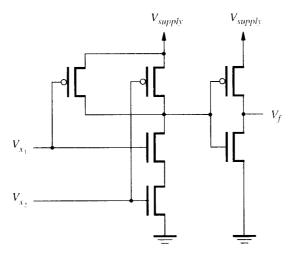

The pull-down network is implemented in the same way as shown in Figures A.11 through A.13. Figure A.17 gives the implementation of a NAND gate, and Figure A.18 gives a NOR gate. Figure A.19 shows how an AND gate is realized by inverting the output of a NAND gate.

In addition to low power dissipation, CMOS circuits have the advantage that MOS transistors can be implemented in very small sizes and thus occupy a very small area on an integrated circuit chip. This results in two significant benefits. First, it is possible to fabricate chips containing millions of transistors, which has led to the realization of modern microprocessors and large memory chips. Second, the smaller the transistor, the faster it can be switched from one state to another. Thus, CMOS circuits can now be operated at speeds in the gigahertz range.

Different CMOS circuits have been developed to operate with power supply voltages in the range from 1.5 to 15 V. The most commonly used power supplies are 5 V and 3.3 V. Circuits that use lower power supply voltages dissipate much less power (power dissipation is proportional to  $V_{supply}^2$ ), which means that more transistors can be placed on a chip without causing overheating. A drawback of lower power supply voltage is reduced noise immunity.

Figure A.17 CMOS realization of a NAND gate.

Figure A.18 CMOS realization of a NOR gate.

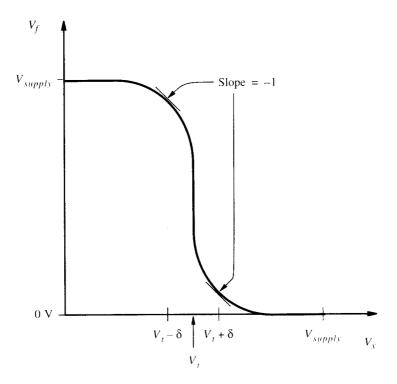

Transitions between low and high signal levels in a CMOS inverter are illustrated in more detail in Figure A.20. The blue curve, known as the *transfer characteristic*, shows the output voltage as a function of the input voltage. The curve indicates that a rather sharp transition in output voltage takes place when the input voltage passes through the value of about  $V_{supply}/2$ . There is a *threshold* voltage,  $V_t$ , and a small value  $\delta$  such that

Figure A.19 CMOS realization of an AND gate.

**Figure A.20** The voltage transfer characteristic for the CMOS inverter.

$V_{out} \approx V_{supply}$  if  $V_{in} < V_t - \delta$  and  $V_{out} \approx 0$  if  $V_{in} > V_t + \delta$ . This means that the input signal need not be exactly equal to the nominal value of either 0 or  $V_{supply}$  to produce the correct output signal. There is room for some error, called *noise*, in the input signal that will not cause adverse effects. The amount of noise that can be tolerated is called the *noise margin*. This margin is  $V_{supply} - (V_t + \delta)$  volts when the logic value of the input is 1, and it is  $V_t - \delta$  when the logic value of the input is 0. CMOS circuits have excellent noise margins.

In this section, we have introduced the basic features of CMOS circuits. For a more detailed discussion of this technology the reader may consult References [1] and [8].

#### **A.5.2** PROPAGATION DELAY

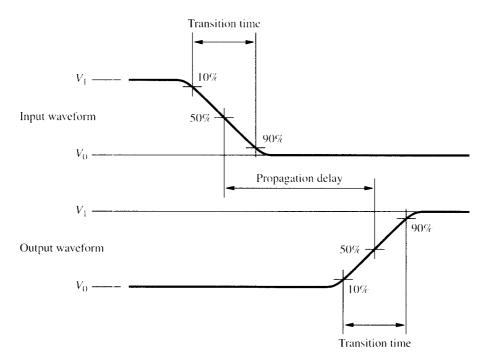

Logic circuits do not switch instantaneously from one state to another. Speed is measured by the rate at which state changes can take place. A related parameter is *propagation delay*, which is defined in Figure A.21. When a state change takes place at the input, a delay is encountered before the corresponding change at the output is observed. This propagation delay is usually measured between the 50-percent points of the transitions, as shown in the figure. Another important parameter is the *transition time*, which is normally measured between the 10- and 90-percent points of the signal swing, as shown. The maximum speed at which a logic circuit can be operated decreases as the

Figure A.21 Definition of propagation delay and transition time.

propagation delay through different paths within that circuit increases. The delay along any path in a logic circuit is the sum of individual gate delays along this path.

#### **A.5.3** FAN-IN AND FAN-OUT CONSTRAINTS

The number of inputs to a logic gate is called its *fan-in*. The number of gate inputs that the output of a logic gate drives is called its *fan-out*. Practical circuits do not allow large fan-in and fan-out because they both have an adverse effect on the propagation delay and hence the speed of the circuit.

Each transistor in a CMOS gate contributes a certain amount of capacitance. As the capacitance increases, the circuit becomes slower and its signal levels and noise margins become worse. Therefore, it is necessary to limit the fan-in and fan-out, typically to a number less than ten. If the number of desired inputs exceeds the maximum fan-in, it is necessary to use an additional gate of the same type. Figure A.9a shows how two gates of the same type can be cascaded. If the number of outputs that have to be driven by a particular gate exceeds the acceptable fan-out, it is possible to use two copies of that gate.

#### A.5.4 TRI-STATE BUFFERS

In the logic gates discussed so far, it is not possible to connect the outputs of two gates together. This would make no sense from the logic point of view because if one gate generated an output value of 1 and the other an output of 0, it would be uncertain what the combined output signal would be. More importantly, in CMOS circuits, the gate that generates the output of 1 establishes a direct path from the output terminal to  $V_{supply}$ , while the gate that generates 0 establishes a path to ground. Thus, the two gates would provide a short circuit across the power supply, which would damage the gates.

Yet, in the design of computer systems, there are many cases where an input signal to a circuit may be derived from one of a number of different sources. This can be done using multiplexer logic circuits, which are discussed in Section A.10. It can also be done using special gates called *tri-state buffers*. A tri-state buffer has three states. Two of the states produce the normal 0 and 1 signals. The third state places the output terminal of the buffer into a high-impedance state in which the output is electrically disconnected from the input it is supposed to drive.

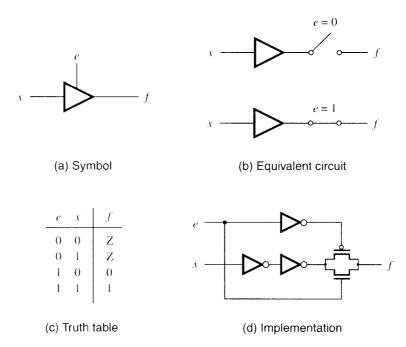

Figure A.22 depicts a tri-state buffer. The buffer has two inputs and one output. The enable input, e, controls the operation of the buffer. When e=1, the output f has the same logic value as the input x. When e=0, the output is placed in the high-impedance state, Z. An equivalent circuit is shown in Figure A.22b. The triangular symbol in this figure represents a noninverting driver. This is a circuit that performs no logic operation because its output merely replicates the input signal. Its purpose is to provide additional electrical driving capability. When combined with the output switch shown in the figure, it behaves according to the truth table given in Figure A.22c. This table describes the required tri-state behavior. Figure A.22d shows a circuit implementation of the tri-state buffer. One NMOS and one PMOS transistor are connected in parallel to implement the switch, which is connected to the output of the driver. Because the two transistor

Figure A.22 Tri-state buffer.

types require complementary control signals at their gate inputs, an inverter is used as shown. When e = 0, both transistors are turned off, resulting in an open switch. When e = 1, both transistors are turned on, resulting in a closed switch.

The driver circuit has to be able to drive a number of inputs of other gates whose combined capacitance may exceed the drive capability of an ordinary logic gate circuit. To provide a sufficient drive capability, the driver circuit needs larger transistors. Hence, the two cascaded NOT gates that realize the driver are implemented with transistors of larger size than in regular logic gates.

The reader may wonder why is it necessary to use the PMOS transistor in the output switch because from the logic function point of view the same behavior could be achieved using just the NMOS transistor. The reason is that these transistors have to "pass" the logic value generated by the driver circuit to the output f, and it turns out that NMOS transistors pass the logic value 0 well but the logic value 1 poorly, while PMOS transistors pass 1 well and 0 poorly. The parallel arrangement of NMOS and PMOS transistors passes both 1s and 0s well. For a more detailed discussion of this issue and tri-state buffers in general, the reader may consult Reference [1].

#### **A.5.5** INTEGRATED CIRCUIT PACKAGES

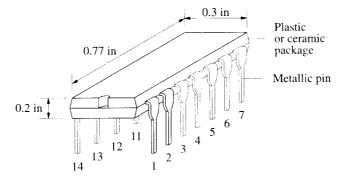

The main features of electronic circuits used to implement logic functions were discussed in previous sections. In practical design, it is necessary to use integrated circuits (ICs) that are commercially available. When ICs became available in the 1960s, there

(a) Physical appearance

(b) Schematic of an integrated circuit providing four 2-input NAND gates

Figure A.23 A 14-pin integrated circuit package.

quickly developed a trend to provide logic gates in the form of standardized IC chips. An IC chip is mounted inside a sealed protective package with a number of metallic pins for external connections. Standard IC packages are available with different numbers of pins. A simple package containing four NAND gates is shown in Figure A.23. The four gates utilize common power supply and ground pins. Such ICs comprising only a few logic gates are referred to as *small-scale integrated* (SSI) *circuits*.

The SSI circuits provide too little functionality for the physical space that they require. Moreover, their performance is inferior because of the electrical characteristics of the pins on an IC package. In general, it is necessary to use larger transistors to provide the signals needed to drive external wires connected to pins. This increases both propagation delay and power dissipation.

A CMOS NAND gate provided as part of an IC package like the one illustrated in Figure A.23 may have a propagation delay of 5 nanoseconds. However, the delay of a NAND circuit inside a large CMOS network implemented on a single chip may be 0.2 ns or less, depending on the manufacturing technology used.

Much larger ICs are available today, and almost all logic circuits are realized with such chips. A chip may implement a useful functional block such as an adder, multiplier, register, encoder, or decoder. But it may also provide just an assortment of gates and programmable interconnection switches that can be configured by the designer to realize a variety of arbitrary functions. In subsequent sections, we will discuss some commonly used functional blocks as well as general user-programmable logic devices.

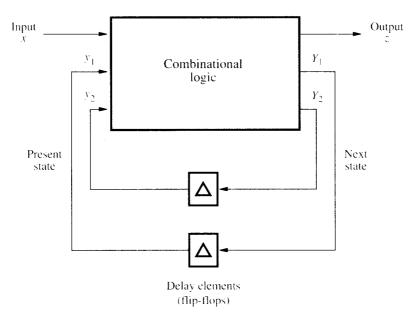

#### A.6 FLIP-FLOPS

The majority of applications of digital logic require the storage of information. For example, a circuit that controls a combination lock must remember the sequence in which the digits are dialed in order to determine whether to open the lock. Another important example is the storage of programs and data in the memory of a digital computer.

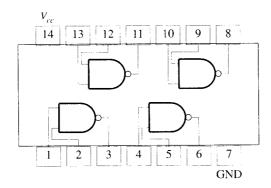

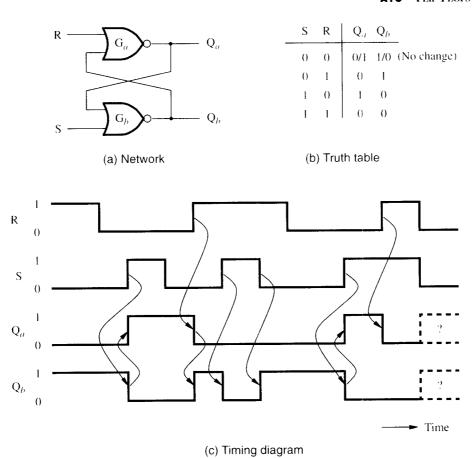

The basic electronic element for storing binary information is termed a *latch*. Consider the two cross-coupled NOR gates in Figure A.24a. Let us examine this circuit, starting with the situation in which R=1 and S=0. Simple analysis shows that  $Q_a=0$  and  $Q_b=1$ . Under this condition, both inputs to gate  $G_a$  are equal to 1. Thus, if R is changed to 0, no change will take place at the outputs  $Q_a$  and  $Q_b$ . If S is set to 1 with R equal to 0,  $Q_a$  and  $Q_b$  will become 1 and 0, respectively, and will remain in this state after S is returned to 0. Hence, this logic circuit constitutes a memory element, or a latch, that remembers which of the two inputs S and R was most recently equal to 1. A truth table for this latch is given in Figure A.24b. Some typical waveforms that characterize the latch are shown in Figure A.24c. The arrows in Figure A.24c indicate the cause-effect relationships among the signals. Note that when the R and S inputs change from 1 to 0 at the same time, the resulting state is undefined. In practice, the latch will assume one of its two stable states at random. The input valuation R=S=1 is not used in most applications of such latches.

Because of the nature of the operation of the preceding circuit, the S and R lines are referred to as the *set* and *reset* inputs. Since the valuation R = S = 1 is normally not used, the  $Q_a$  and  $Q_b$  are usually represented by Q and  $\overline{Q}$ , respectively. However,  $\overline{Q}$  should be regarded merely as a symbol representing the second output of the latch rather than as the complement of Q, because the input valuation R = S = 1 yields  $Q = \overline{Q} = 0$ .

#### A.6.1 GATED LATCHES

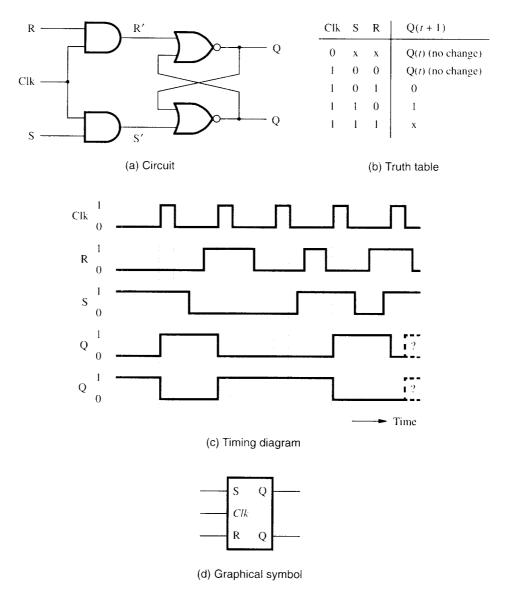

Many applications require that the time at which a latch is set or reset be controlled from an input other than R and S, termed a *clock* input. The resulting configuration is called a *gated SR latch*. A logic circuit, truth table, characteristic waveforms, and a graphical symbol for such a latch are given in Figure A.25. When the clock, Clk, is equal to 1, points S' and R' follow the inputs S and R, respectively. On the other hand, when Clk = 0, the S' and R' points are equal to 0, and no change in the state of the latch can take place.

Figure A.24 A basic latch implemented with NOR gates.

So far we have used truth tables to describe the behavior of logic circuits. A truth table gives the output of a network for various input valuations. Logic circuits whose outputs are uniquely defined for each input valuation are referred to as *combinational circuits*. This is the class of circuits discussed in Sections A.1 to A.4. When memory elements are present, a different class of circuits is obtained. The output of such circuits is a function not only of the present valuation of the input variables but also of their previous behavior. An example of this is shown in Figure A.24. Circuits of this type are called *sequential circuits*.

Because of the memory property, the truth table for the latch has to be modified to show the effect of its present state. Figure A.25*b* describes the behavior of the gated SR latch, where Q(t) denotes its present state. The transition to the next state, Q(t+1), occurs following a clock pulse. Note that for the input valuation S = R = 1, Q(t+1) is undefined for reasons discussed earlier.

Figure A.25 Gated SR latch.

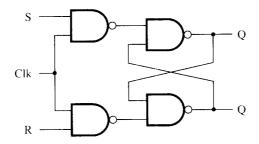

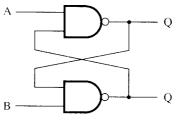

The gated SR latch can be implemented using NAND gates as shown in Figure A.26. It is a useful exercise to show that this circuit is functionally equivalent to the circuit in Figure A.25*a* (see Problem A.20).

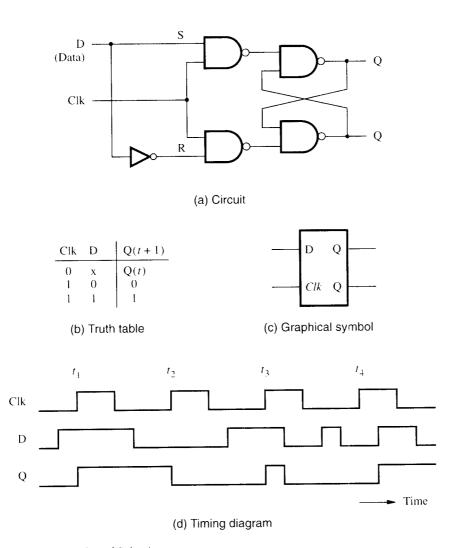

A second type of gated latch, called the *gated D latch*, is shown in Figure A.27. In this case, the two signals S and R are derived from a single input D. At a clock pulse,

**Figure A.26** Gated SR latch implemented with NAND gates.

Figure A.27 Gated D latch.

the Q output is set to 1 if D = 1 or is reset to 0 if D = 0. This means that the D flip-flop samples the D input at the time the clock is high and stores that information until a subsequent clock pulse arrives.

#### **A.6.2** MASTER-SLAVE FLIP-FLOP

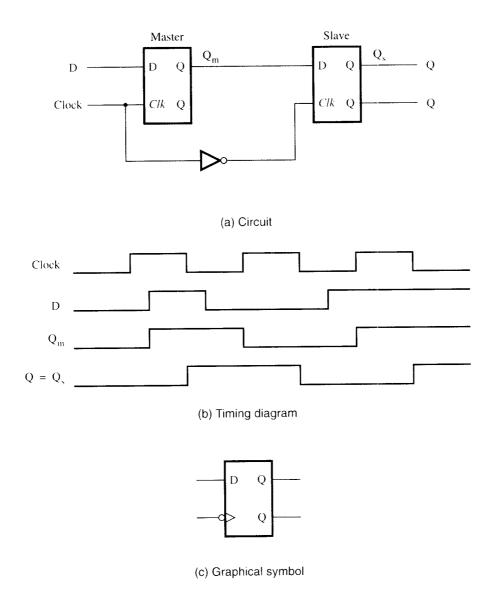

In the circuit of Figure A.25, we assumed that while Clk = 1, the inputs S and R do not change. Inspection of the circuit reveals that the outputs will respond immediately to any change in the S or R input during this time. Similarly, for the circuit of Figure A.27. Q = D while Clk = 1. This is undesirable in many cases, particularly in circuits involving counters and shift registers, which will be discussed later. In such circuits, immediate propagation of logic conditions from the data inputs (R, S, and D) to the latch outputs may lead to incorrect operation. The concept of a master-slave organization eliminates this problem. Two gated D latches can be connected to form a master-slave D flip-flop, as shown in Figure A.28a. The first, referred to as the master, is connected to the input line D when Clock = 1. A 1-to-0 transition of the clock isolates the master from the input and transfers the contents of the master stage to the slave stage. We can see that no direct path ever exists from the input D to the output Q.

It should be noted that while Clock = 1, the state of the master stage is immediately affected by changes in the input D. The function of the slave stage is to hold the value at the output of the flip-flop while the master stage is being set up to the next-state value determined by the D input. The new state is transferred from the master to the slave after the 1-to-0 transition on Clock. At this point, the master stage is isolated from the inputs so that further changes in the D input will not affect this transfer. Examples of state transitions are shown in the form of a timing diagram in Figure A.28b.

The term *flip-flop* refers to a storage element that changes its output state at the edge of a controlling clock signal. In the above master-slave D flip-flop, the observable change takes place at the negative (1-to-0) edge of the clock. The change is observable when it reaches the Q terminal of the slave stage. Note that in the circuit in Figure A.28 we could have used the complement of Clock signal to control the master stage and the uncomplemented Clock to control the slave stage. In that case, the changes in the flip-flop output Q would occur at the positive edge of the clock.

A graphical symbol for a flip-flop is given in Figure A.28c. We have used an arrowhead, instead of the label Clk, to denote the clock input to the flip-flop. This is a standard way of denoting that the positive edge of the clock causes changes in the state of the flip-flop. In our figure it is the negative edge which causes changes, so a small circle is used (in addition to the arrowhead) on the clock input.

#### **A.6.3** EDGE TRIGGERING

A flip-flop is said to be *edge triggered* if data present at the input are transferred to the output only at a transition in the clock signal. The input and output are isolated from each other at all other times. The terms *positive* (*leading*) *edge triggered* and *negative* (*trailing*) *edge triggered* describe flip-flops in which data transfer takes place at the

Figure A.28 Master-slave D flip-flop.

0-to-1 and the 1-to-0 clock transitions, respectively. For proper operation, edge-triggered flip-flops require the triggering edge of the clock pulse to be well defined and to have a very short transition time. The master-slave flip-flop in Figure A.28 is negative-edge triggered.

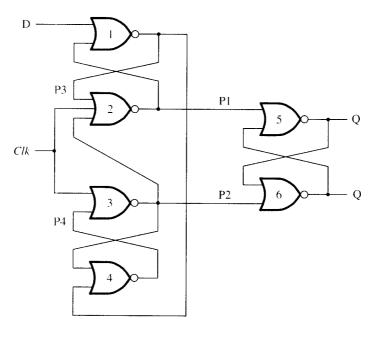

A different implementation for a negative edge-triggered D flip-flop is given in Figure A.29a. Let us consider the operation of this flip-flop. If Clk = 1, the outputs

(a) Network

Figure A.29 A negative edge-triggered D flip-flop.

of gates 2 and 3 are both 0. Therefore, the flip-flop outputs Q and  $\overline{Q}$  maintain the current state of the flip-flop. It is easy to verify that during this period, points P3 and P4 immediately respond to changes at D. Point P3 is kept equal to  $\overline{D}$ , and P4 is maintained equal to D. When Clk drops to 0, these values are transmitted to P1 and P2 by gates 2 and 3, respectively. Thus, the output latch, consisting of gates 5 and 6, acquires the new state to be stored.

We now verify that while Clk = 0, further changes at D do not change points P1 and P2. Consider two cases. First, suppose D = 0 at the negative edge of Clk. The 1 at P2 maintains an input of 1 at each of the gates 2 and 4, holding P1 and P2 at 0 and 1, respectively, independent of further changes in D. Second, suppose D = 1 at the negative edge of Clk. The I at P1 means that further changes at D cannot affect the output of gate I, which is maintained at 0.

When *Clk* goes to 1 at the start of the next clock pulse, points P1 and P2 are again forced to 0, isolating the output from the remainder of the circuit. Points P3 and P4 then follow changes at D, as we have previously described.

An example of the operation of this type of D flip-flop is shown in Figure A.29b. The state acquired by the flip-flop upon the 1 to 0 transition of Clk is equal to the value on the D input immediately preceding this transition. However, there is a critical time period  $T_{CR}$  around the negative edge of Clk during which the value on D should not change. This region is split into two parts, the *setup time* before the clock edge and the *hold time* after the clock edge, as shown in the figure. The timing diagram shows that the output Q changes slightly after the negative edge of the clock. This is the effect of the propagation delay through the NOR gates.

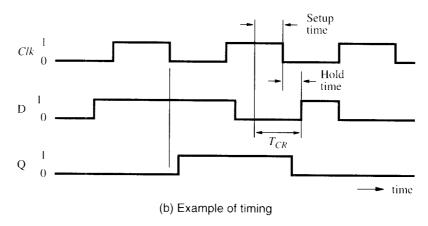

## A.6.4 T FLIP-FLOP

The most commonly used flip-flops are the D flip-flops because they are useful for temporary storage of data. However, there are applications for which other types of flip-flops are convenient. Counter circuits, discussed in Section A.8, are implemented efficiently using T flip-flops. A *T flip-flop* changes its state every clock cycle if its input T is equal to 1. We say that it "toggles" its state.

Figure A.30 presents the T flip-flop. Its circuit is derived from a D flip-flop as shown in Figure A.30a. Its truth table, graphical symbol, and a timing diagram example are also given in the figure. Note that we have assumed a positive edge-triggered flip-flop.

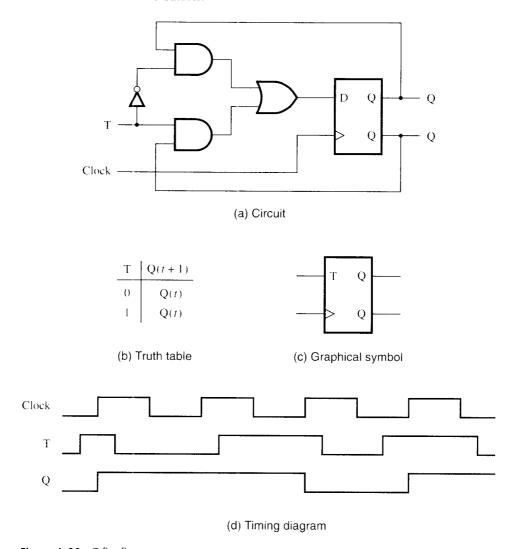

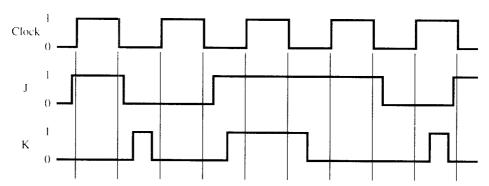

### A.6.5 JK FLIP-FLOP

Another flip-flop that is sometimes encountered in practice is the *JK flip-flop*, which combines the behaviors of SR and T flip-flops. It is presented in Figure A.31. Its operation is defined by the truth table in Figure A.31*b*. The first three entries in this table define the same behavior as those in Figure A.25*b* (when C/k = 1), so that J and K correspond to S and R. For the input valuation J = K = 1, the next state is defined as the complement of the present state of the flip-flop. That is, when J = K = 1, the flip-flop functions as a *toggle*, reversing its present state.

A JK flip-flop can be implemented using a D flip-flop connected such that

$$D = J\overline{O} + \overline{K}O$$

The corresponding circuit is shown in Figure A.31a.

The JK flip-flop is versatile. It can be used to store data, just like the D flip-flop. It can also be used to build counters, because it behaves like the T flip-flop if its J and K input terminals are connected together.

Figure A.30 T flip-flop.

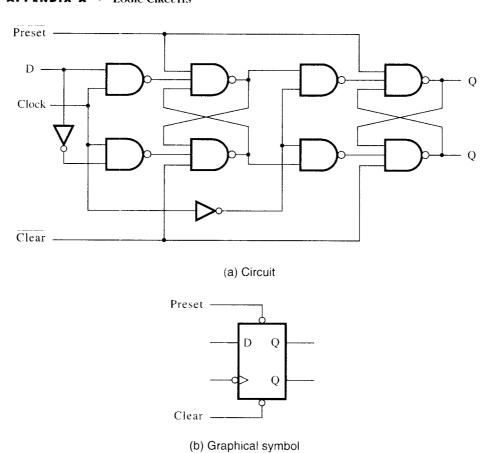

# A.6.6 FLIP-FLOPS WITH PRESET AND CLEAR

The state of a flip-flop is determined by its present state and the logic values on its input terminals. Sometimes it is desirable to force a flip-flop into a particular state, either 0 or 1, regardless of its present state and the values of the normal inputs. For example, when a computer is powered on, it is necessary to place all flip-flops into a known state. Usually, this means resetting their outputs to state 0. In some cases it is desirable to preset some flip-flops into state 1.

(b) Truth table

(c) Graphical symbol

Figure A.31 JK flip-flop.

Figure A.32 illustrates how preset and clear control inputs can be added to a master-slave D flip-flop, to force the flip-flop into state 1 or 0 independent of the D input and the clock. These inputs are active low, as indicated by the overbars and bubbles in the figure. When both the Preset and Clear inputs are equal to 1, the flip-flop is controlled by the clock and D input in the normal way. When  $\overline{\text{Preset}} = 0$ , the flip-flop is forced to the 1 state, and when  $\overline{\text{Clear}} = 0$ , the flip-flop is forced to the 0 state. The preset and clear controls are also often incorporated in the other flip-flop types.

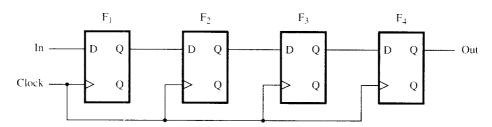

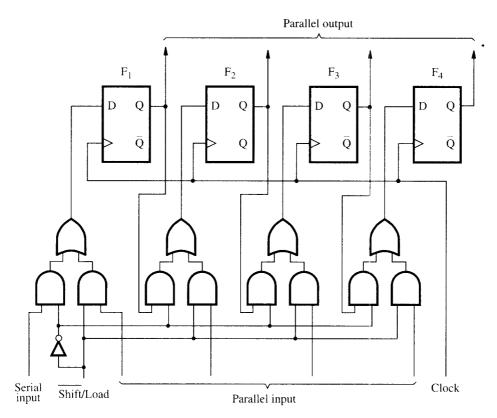

# **A.7** REGISTERS AND SHIFT REGISTERS

An individual flip-flop can be used to store one bit. However, in machines in which data are handled in words consisting of many bits (perhaps as many as 64), it is convenient to arrange a number of flip-flops into a common structure called a *register*. The operation of all flip-flops in a register is synchronized by a common clock. Thus, data are written (loaded) into or read from all flip-flops at the same time.

Figure A.32 Master-slave D flip-flop with Preset and Clear.

Figure A.33 A simple shift register.

Processing of digital data often requires the capability to shift and rotate the data, so it is necessary to provide the hardware with this facility. A simple mechanism for realizing both operations is a register whose contents may be shifted to the right or left one bit position at a time. As an example, consider the 4-bit shift register in Figure A.33. It consists of D flip-flops connected so that each clock pulse will cause the transfer of

the contents (state) of  $F_i$  to  $F_{i+1}$ , effecting a "right shift." Data are shifted serially into and out of the register. A rotation of the data can be implemented by connecting Out to In.

Proper operation of a shift register requires that its contents be shifted exactly one position for each clock pulse. This places a constraint on the type of storage elements that can be used. Gated latches, depicted in Figure A.27, are not suitable for this purpose. While the clock is high, the value on D input quickly propagates to the output. From there, the value propagates through the next gated latch in the same manner. Hence, there is no control over the number of shifts that will take place during a single clock pulse. This number depends on the propagation delays of the gated latches and the duration of the clock pulse. The solution to the problem is to use either the master-slave or the edge-triggered flip-flops.

A particularly useful form of a shift register is one that can be loaded and read in parallel. This can be accomplished with some additional gating as illustrated in Figure A.34, which shows a 4-bit register constructed with D flip-flops. The register can be loaded either serially or in parallel. When the register is clocked, a shift takes place if  $\overline{\text{Shift}}/\text{Load} = 0$ ; otherwise, a parallel load is performed.

Figure A.34 Parallel-access shift register.

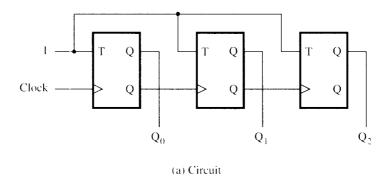

#### **A.8 COUNTERS**

In the preceding section, we discussed the applicability of flip-flops in the construction of shift registers. They are equally useful in the implementation of *counter* circuits. It is hardly necessary to justify the need for counters in digital machines. In addition to being hardware mechanisms for realizing ordinary counting functions, counters are also used to generate control and timing signals. A counter driven by a high-frequency clock can be used to produce signals whose frequencies are submultiples of the original clock frequency. In such applications a counter is said to be functioning as a scaler.

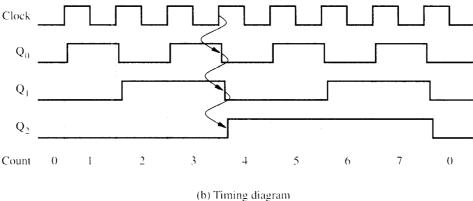

A simple three-stage (or 3-bit) counter constructed with T flip-flops is shown in Figure A.35. Recall that when the T input is equal to 1, the flip-flop acts as a toggle, that is, its state changes with each successive clock pulse. Thus, two clock pulses will cause Q<sub>0</sub> to change from the 1 state to the 0 state and back to the 1 state or from 0 to 1 to 0. This means that the output waveform of  $Q_0$  has half the frequency of the clock. Similarly, because the second flip-flop is driven by  $Q_0$ , the waveform at  $Q_1$  has half the frequency of Q<sub>0</sub>, or one-fourth the frequency of the clock. Note that we have assumed that the positive edge of the clock input to each flip-flop triggers the change of its state.

Figure A.35 A 3-bit up-counter.

Such a counter is often called a *ripple counter* because the effect of an input clock pulse ripples through the counter. For example, the positive edge of pulse 4 will change the state of  $Q_0$  from 1 to 0. This change in  $Q_0$  will then force  $Q_1$  from 1 to 0, which in turn forces  $Q_2$  from 0 to 1. If each flip-flop introduces some delay  $\Delta$ , then the delay in setting  $Q_2$  is  $3\Delta$ . Such delays can be a problem when very fast operation of counter circuits is required. In many applications, however, these delays are small in comparison with the clock period and can be neglected.

With the addition of some extra logic gates, it is possible to construct a "synchronous" counter in which each stage is under the control of the common clock so that all flip-flops can change their states simultaneously. Such counters are capable of operation at higher speed because the total propagation delay is reduced considerably. In contrast, the counter in Figure A.35 is said to be "asynchronous."

# A.9 DECODERS

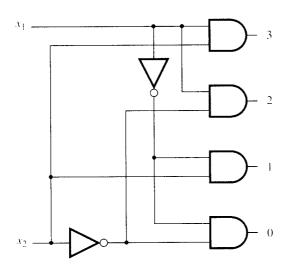

Much of the information in computers is handled in a highly encoded form. In an instruction, an n-bit field may be used to denote 1 out of  $2^n$  possible choices for the action to be taken. To perform the desired action, the encoded instruction must first be decoded. A circuit capable of accepting an n-variable input and generating the corresponding output signal on one out of  $2^n$  output lines is called a *decoder*. A simple example of a two-input to four-output decoder is given in Figure A.36. One of the four output lines is selected by the inputs  $x_1$  and  $x_2$ , as indicated in the figure. The selected output has the logic value 1, and the remaining outputs have the value 0.

Other useful types of decoders exist. For example, using information in BCD form often requires decoding circuits in which a four-variable BCD input is used to select

| $x_1$ $x_2$ | Active output |

|-------------|---------------|

| 0 0         | 0             |

| 0 1         | 1             |

| 1 0         | 2             |

| 1 1         | 3             |

Figure A.36 A two-input to four-output decoder.

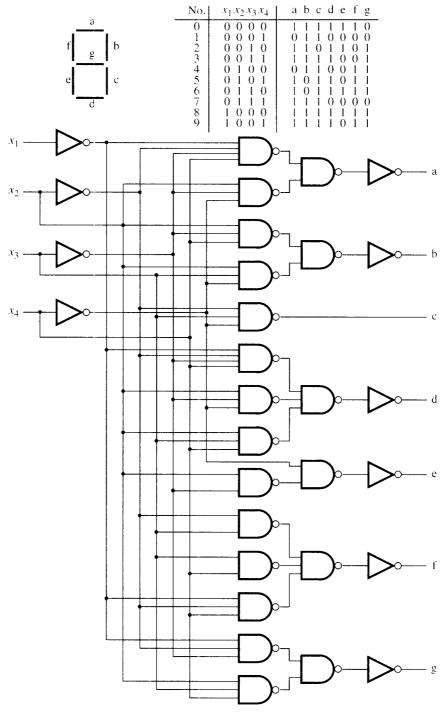

Figure A.37 A BCD to seven-segment display decoder.

1 out of 10 possible outputs. As another specific example, let us consider a decoder suitable for driving a seven-segment display. Figure A.37 shows the structure of a seven-segment element used for display purposes. We can easily see that any decimal number from zero to nine can be displayed with this element simply by turning some segments on (light) while leaving others off (dark). The necessary functions are indicated in the table. They can be realized using the decoding circuit shown in the figure. Note that the circuit is constructed with NAND gates. We encourage the reader to verify that the circuit implements the required functions.

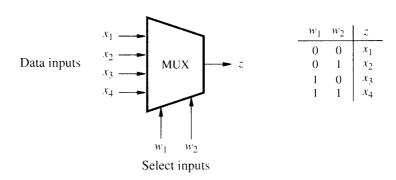

# A.10 MULTIPLEXERS

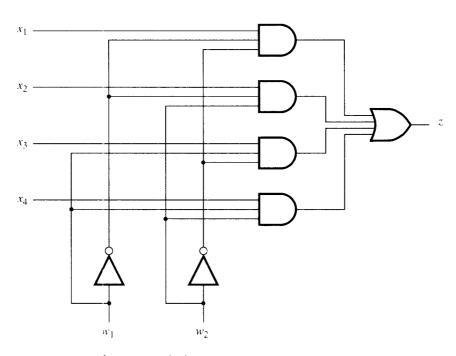

In the preceding section, we saw that decoders select one output line on the basis of input signals. The selected output line has logic value 1, while the other outputs have the value 0. Another class of very useful selector circuits exists in which any one of n data inputs can be selected to appear as the output. The choice is governed by a set of "select" inputs. Such circuits are called *multiplexers*. An example of a multiplexer circuit is shown in Figure A.38. It has two select inputs,  $w_1$  and  $w_2$ . Their four possible valuations are used to select one of four inputs,  $x_1, x_2, x_3$ , or  $x_4$ , to appear as the output z. A simple logic circuit that can implement the required operation is also given. Obviously, the same structure can be used to realize larger multiplexers, in which k select inputs are used to connect one of the  $2^k$  data inputs to the output.

The obvious application of multiplexers is in the gating of data that may come from a number of different sources. For example, loading a 16-bit data register from one of four distinct sources can be accomplished with sixteen 4-input multiplexers.

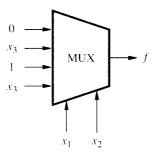

Multiplexers are also very useful as basic elements for implementing logic functions. Consider a function f defined by the truth table of Figure A.39. It can be represented as shown in the figure by factoring out the variables  $x_1$  and  $x_2$ . Note that for each valuation of  $x_1$  and  $x_2$ , the function f corresponds to one of four terms:  $0, 1, x_3,$  or  $\overline{x}_3$ . This suggests the possibility of using a four-input multiplexer circuit, in which  $x_1$  and  $x_2$  are the two select inputs that choose one of the four data inputs. Then, if the data inputs are connected to  $0, 1, x_3,$  or  $\overline{x}_3$  as required by the truth table, the output of the multiplexer will correspond to the function f. The approach is completely general. Any function of three variables can be realized with a single four-input multiplexer. Similarly, any function of four variables can be implemented with an eight-input multiplexer, and so on.

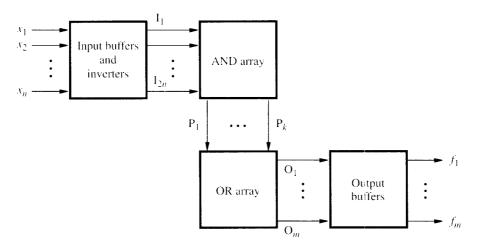

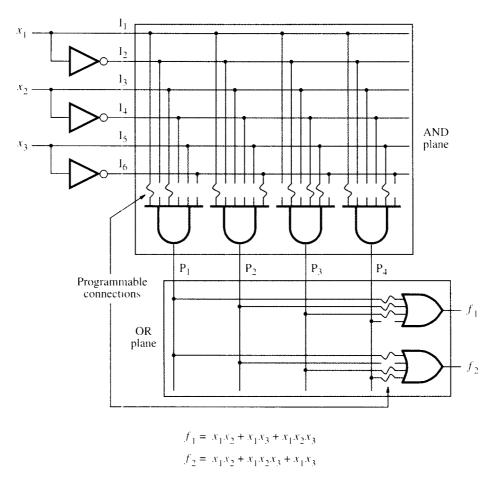

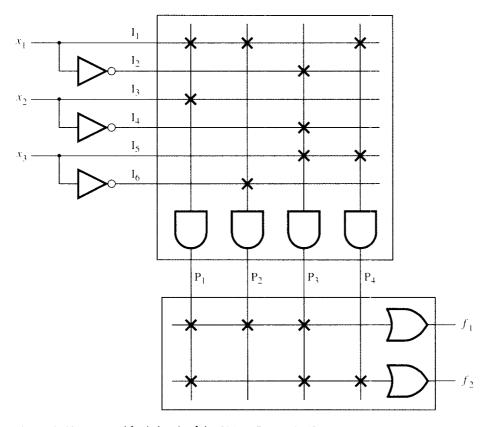

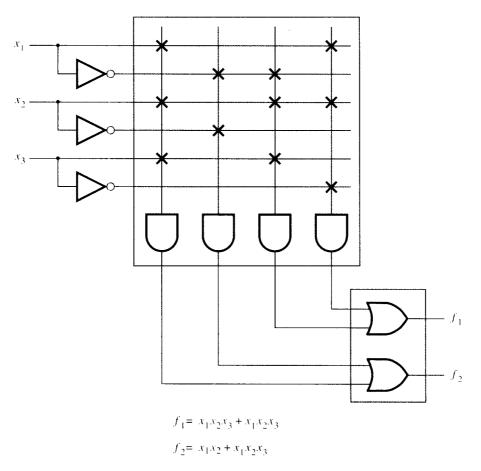

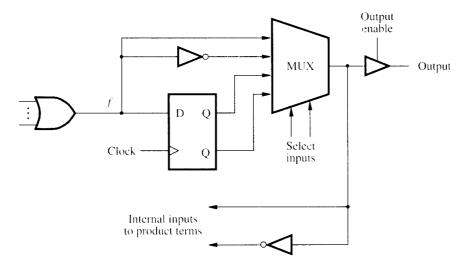

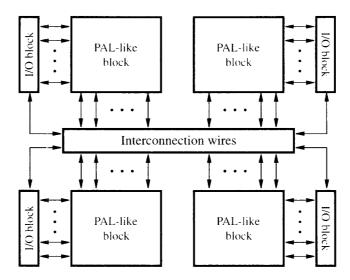

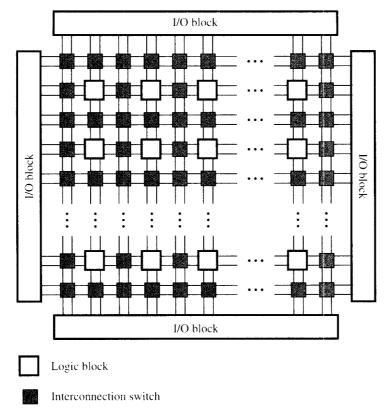

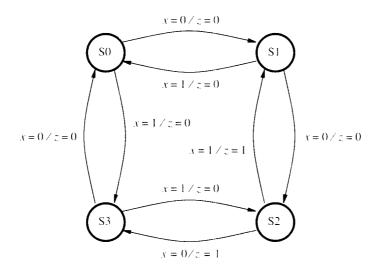

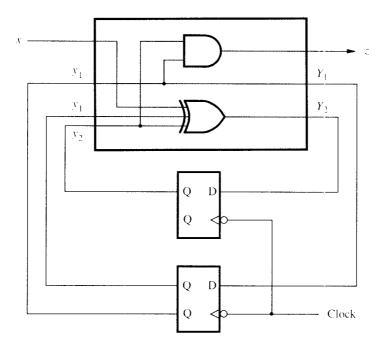

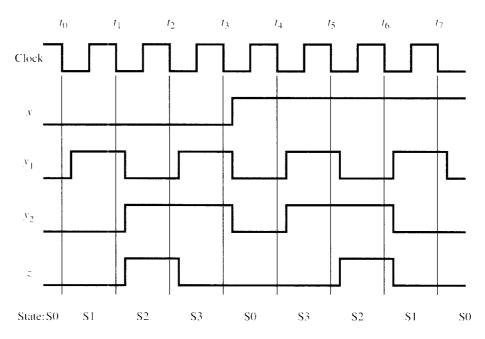

# **A.11** PROGRAMMABLE LOGIC DEVICES (PLDS)